# Advanced Architectural Innovations In Double-Gate Mosfets For Enhanced Performance In Vlsi Applications

Rani Kiran<sup>1</sup>, Imran Ullah Khan<sup>2</sup>\*, S. Hasan Saeed<sup>3</sup>

<sup>1,2& 3</sup>Department of Electronics & Communication Engg., Integral University, Lucknow, India

<sup>a</sup>rkiran041@gmail.com, <sup>b</sup>iukhan@iul.ac.in, ssaeed@iul.ac.in Corresponding Author Email: iukhan@iul.aac.in

Cylindrical Surrounding Double-Gate Metal Oxide Semiconductor Field Effect Transistors (CSDG MOSFETs) are crucial in minimizing thermal effects since they carry a cylindrical configuration that lowers heat generation and provides adequate stability. Therefore, this present study is carried out on the thermal impacts upon CSDG MOSFETs for nanotechnology applications and VLSI circuits. The research analyzes different aspects of CSDG MOSFETs: Thermal resistance, carrier mobility transconductance and overall thermal stability. The results showed the detection of the inner cylinder as well as outer radial section of resistors inside the CSDG MOSFET heat dissipation system's surface coiling turns at 25°C and carry out their tests at this temperature level with operational DC current flow parameters not more than RMS Actual Value. The paper applies a thermal resistance model to evaluate power distribution and discusses the occurrence of thermal noise especially in nanoscale design as well as two-channel designs. For thermal noise analysis, the study uses a Charge-based PSD method that accommodates factors such as channel length and carrier mobility. The research also scrutinises temperature effects on critical parameters like Thermal Resistance (TR), Drain Current (Im), Transconductance (TC) and carrier mobility. It shows that these parameters are very sensitive to temperature changes because while the higher temperatures improve drift current, decrease electron mobility due to high collision frequency. Improvement strategies such as a control circuit in the MOSFET and encompassing cylindrical design have been introduced for better thermal management. The study concludes that CSDG MOSFET designs are more effective at handling thermal impacts than conventional ones making them desirable for high-performing electronic appliances, especially in areas with oscillating temperatures. This comprehensive account outlines the potential of CSDGM; devices to improve the integrity and performance based on VLSI and nanotechnology, thus opening opportunities for bettering future.

**Keywords:** CSDG MOSFET, Thermal Resistance, Drain Current Analysis, Trans conductance Variation, Temperature Sensitivity, Thermal Stability, Numerical Simulation, Carrier Mobility.

#### Introduction

All manuscripts must be in English, also the table and figure text.

Please keep a second copy of your manuscript in your office. When receiving the paper, we assume that the corresponding authors grant us the copyright to use the paper for the book or journal in question. Should authors use tables or figures from other Publications, they must ask the corresponding publishers to grant them the right to publish this material in their paper.

Use italic for emphasizing a word or phrase. Do not use boldface typing or capital letters except for section headings (cf. remarks on section headings, below).

It is fabricated using MOSFET due to its relatively easy design, energy-efficient capabilities, and the simplified manufacturing process of VLSI Circuits. Such features are necessary for portable electronics development [1] and [2]. In contrast, MOSFETs are prone to temperature fluctuations, which may affect their functionality. Tremendously high temperatures affect the molecular motion of carriers within the MOSFET so that speed and functionality fall. Poor temperature management can lead to thermal runaway, a self-reinforcing process between increased temperature and leakage current, causing instability in the MOSFET [3].

High temperatures in MOSFETs, especially when combined with a high voltage supply, as is the case in this study, can result in low values of both drain saturation current and switching speed rates [4]. On the other hand, lower temperatures increase device transconductance and reduce series resistance, which results in better dynamics. These lower temperatures also reduce sub-threshold current and slope, saving power consumption [5]. Nevertheless, the disadvantages of lower temperatures, such as reduced efficiency and reliability, usually prevail over these advantages, which make thermal effects a critical issue [6].

[7] and [8] have assessed the thermal conductivity of MOSFETs with a 65 nm channel length BOX SiO2 in their study. The researchers compared high-k dielectric materials, including diamond and  $Al_2O_3$ , to the conventional SiO<sub>2</sub>. Furthermore, they examined low-k materials such as air. This study found that substituting BOX with materials such as diamond, which has a thermal conductivity of 800 Wm-1K-1, or using AlN and  $Al_2O_3$  with lower thermal conductivities improves thermal sensitivity and worsens short-channel effects.

[8] and [9] also helped to understand and solve the thermal problems of MOSFET. To achieve better control over the channels, multi-gate transistors were introduced to mitigate thermal effects and reduce leakage current [10] and [11]. Despite these developments, thermal effects still need to be solved. Figure 1 led to a new architecture, namely CSDG MOSFET [12] and [13]. This design significantly decreases the role of the corner effect on "carrier mobility" [14] and reduces contact between the device and the IC board; thus, the generated heat is minimised.

Fig 1: Internal view of 3D CSDG MOSFET [1]

## Thermal Resistances in CSDG MOSFET

In our study of the thermal resistances in "Cylindrical Surrounding Double-Gate (CSDG) MOSFET", we have considered earlier models that discuss heat management and their limitations cited in [15] and [16]. The low gate TR ( $R_{\rm E}$ ) of the CSDG MOSFET impacts the power distribution across the interior and exterior cylindrical shapes. The thermal resistance model covers the channel source and drain total resistance but pays little attention to the MOSFET body. The thermal resistance within the inside cylindrical section ( $R_{\rm g}$ ) and the external cylindrical section ( $R_{\rm gext}$ ) can be expressed as follows:

For the internal part:

$$R = R + R + R + R$$

(1)

For the external part:  $R = R + R + R$  (2)  $R + R$  (2)

Nanotechnology Perceptions 20 No. S11 (2024)

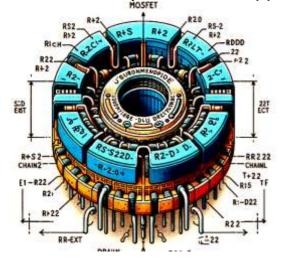

## Fig. 2: Internal Cylindrical Part [2]

Fig. 2 includes the internal cylindrical section (labeled  $R\phi$ ) and the external cylindrical section (labeled R¢ext), along with their respective components such as source, channel, and drain. The total thermal resistance R€ is also denoted.

The following symbols denote the respective resistances of sources  $R_{\varphi}$  and  $R_{\varphi ext}$ , channel R<sub>¢CH</sub> and R<sub>¢CH(2)</sub>, and drains for both exterior and interior components as R<sub>¢D</sub> and  $R_{\phi D(2)}$ .

Considering the parallel arrangement of its interior and exterior, the total TR, referred to as "CSDG MOSFET", is found.

$$R_{\epsilon} = \frac{[(R_{\epsilon}S + R_{\epsilon}CH + R_{\epsilon}D)(R_{\epsilon}S(2) + R_{\epsilon}CH(2) + R_{\epsilon}D(2))]}{[(R_{\epsilon}S + R_{\epsilon}CH + R_{\epsilon}D) + (R_{\epsilon}S(2) + R_{\epsilon}CH(2) + R_{\epsilon}D(2))]}$$

(3)

$R_{\epsilon}$  represents a total thermal resistance

By this study, the paralleling of these "CSDG MOSFETs" effectively reduces thermal resistance; thus, this value is lower than other previously investigated "MOSFETs". The lower TR in the CSDG MOSFET is beneficial mainly when used in nanotechnology.

## Thermal Noise (TN) in CSDG MOSFET

Decrease in dimension of MOSFETs, increases TN, this in turn affects their operating efficiency. Specifically, the CSDG MOSFET features dual-channel architecture and functions at the nanoscale [17] and [18]. Contrary to popular belief, the thermal noise in short-channel MOSFETs does not exceed too much compared to more extended channels [19] and [20]. In CSDG MOSFETs, the thermal noise remains significant even with zero gate voltages as they have nanoscale dimensions and dual-channel configuration.

A new methodology is presented to reduce the TNin CSDG MOSFETs. This approach uses the charged-based "Power Spectrum Density (PSD)" technique to assess the TN of MOSFETs. As references [21] and [22] state, the thermal noise is affected by charge carrier mobility, temperature, total charge along the channel, and channel length. This model intended for long-channel MOSFET is well applicable to short-channel CSDG MOSFETs because of their high transconductance values. It is expressed as:  $\epsilon = \frac{4\alpha\tau\Thetaq}{W^2}$

$$\epsilon = \frac{4\alpha\tau\Thetaq}{W^2}$$

τ denote the charge carrier mobility

$\Theta$  the temperature

W represents length of the channel.

In this model, the charge flow across channels is mostly unaffected by the "drift current (v<sub>r</sub>)." However, the prevalence of "diffusive random current (DRC)" in charge transport has a direct influence on the increase of thermal noise in this device. This is particularly true in the case of CSDG MOSFET's linear (ohmic) region.

A critical element in the progressive channel region of CSDG MOSFETs is carrier mobility loss due to lateral electric fields, which greatly influence thermal noise in these devices [31]. The thermal noise might be represented or simulated as:

$$\epsilon_n^2 = 4pq^2G\Delta \varphi \frac{H}{W}$$

(5)

p-carrier density

G-Diffusion constant.

$\Delta \phi$  - Band width

H- Channel width

I<sub>m</sub> is influenced by reduced carrier mobility (CM), is computed as:

$$I_{m=} \text{TpHq(V)} \frac{\partial V}{\partial W} / \left(1 + \frac{\frac{\partial V}{\partial W}}{F_{\_B}}\right)$$

(6)

By performing the process of integration about the applied voltage along the channels, the noise levels are transformed:

$$\Delta I_m = \epsilon_n \frac{\tau_{pHq}(V)\Delta V}{W + \frac{Vds}{F\_B}}$$

(7)

This equation accounts for the amount of charges, channel charge, mobility and width of the gate voltages applied for CSDG MOSFET. Thus, the total noise for two "CSDG MOSFET's" channels is presented below.

$$e_n^2 = \sum_{(8)} [\Delta I_m]^2$$

$$e_n = \sum 4pq 2G\Delta \varphi \frac{H}{W} \cdot \frac{gth \Delta V2}{W + \frac{Vds}{F\_B}}$$

(9)

This study focuses on the increased Thermal noise current in CSDG MOSFETs caused by carrier heating effects at high applied voltages and in the gradual channel approximation. This is relevant to using these devices in nanotechnology applications, where thermal noise plays a crucial role in performance.

## Thermal Impact on the CSDG MOSFET Parameters

The efficiency and performance of MOSFETs are highly influenced by temperature changes [23]. Self-heating in these devices can change their operating environment and, consequently, their effectiveness and reliability. However, an improved CSDG MOSFET design has been developed with these constraints: a cylindrical structure to reduce board contact and heat generation.

This analytical study focuses on the CSDG MOSFET regarding critical parameters such as Im, electron mobility (Em), and  $T_c$ . The research looks at how temperature changes impact these parameters. The estimation of the CSDG MOSFET device's overall performance is contingent upon the temperature-dependent parameters, which is computed using mathematical modelling.

#### **Thermal Effect on Drain Current**

The rise in temperature affects the movement of electrons, which also impacts the drain current for MOSFETs. The only crucial scattering mechanism in the context of undoped CSDG MOSFET channels is electron-electron collisions.

An increase in temperature boosts the drift current. Applying voltage across the CSDG MOSFET gates generates an electric field along the channels, exciting the electrons. However, when the temperature increases, an initial rise in the speed of electrically charged particles is observed. There is a gradual decrease in electron mobility over time due to the higher collision frequency inside cylindrical channels. This slows down the speed at which electrons move from the source to the drain. The relationship between the drift velocity  $(v_r)$  and the carrier mobility CM is directly established by references [22] and [23]

$$v_r = \tau \cdot F$$

(10)

$$I_r = \frac{pq\tau 2\pi(c+d)V}{W}$$

(11)

V-Voltage applied.

W- Channel length

$$I_{\text{diff} = E' q} \pi(c+d)^2 \left[ -\frac{dp}{dW} \right]$$

(12)

$I_{\text{diff}}$  represents the diffusion current,

E' is the "diffusion constant"

$$E' = \tau \Psi \tag{13}$$

$\Psi$  -Thermal voltage.

$$\Psi = \frac{h\Theta}{q}$$

(14)

h - Boltzmann's constant

Θ- temperature

## **Thermal Effect on Transconductance**

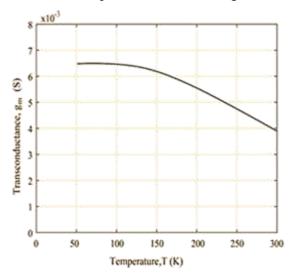

Figure 3 analyze the CSDG MOSFET's transconductance is crucial, especially when assessing how sensitive it is to temperature. Transconductance measures the relationship between the current transfer from the drain and the voltage across the gate and source. This value can be obtained by utilising "the derivative of the Im" with refer to "the gate-source voltage", When the  $V_{ds}$  is constant. Equations (5) & (6) illustrate this method.

The transconductance, confirmed through simulation, illustrates a notable increase with a decrease in temperature, aligning with the behaviour observed in saturation current. Transconductance remains relatively stable with temperature variations up to approximately 100 K. Beyond this point, a gradual decrease is observed, becoming more pronounced past 150 K. This pattern suggests that while the CSDG MOSFET demonstrates efficiency at

temperatures below 100 K, its reliability diminishes at temperatures exceeding 150 K. Future sections will explore measures to mitigate this issue.

Fig. 3: Thermal Effect on Transconductance

# Thermal Effect on Carrier Mobility (CM)

Temperature primarily affects the conducting channels' Em in the CSDG MOSFET. The Em is indicator of gadget's efficiency. CM is influenced by elements such as "Electric Field Strength", different scattering mechanisms, and temperature. The low "threshold voltage" is the distinguishing characteristic of the CSDG MOSFET, which leads to an increase in Em until it reaches a saturation point, at which time Im stabilises.

The ideal length of the conducting channels and the undoped state are two essential components of this complex MOSFET design. The absence of impurity doping minimizes several scattering mechanisms, even though electron-electron collision is still the primary factor. Temperature is an essential indicator of mobility. The correlation between increasing temperature and rising drift current and carrier mobility has been proven at cryogenic temperatures.

$$F = \frac{\lambda(c+d)}{2\pi c d\sigma}$$

(15)

F– Electric Field

$\lambda$  – electron per unit

c, d-internal and external radii

$\sigma$  - permittivitty

v<sub>r</sub>- drift velocity

$$\tau = \frac{2\pi\sigma}{\lambda} \left[ \frac{\text{cd}}{\text{c+d}} \right] \qquad v_{\text{rCSDG}}$$

(16)

$$\tau = \frac{2\pi\sigma}{\lambda\Theta} \left[ \frac{cd}{c+d} \right] \qquad v_{rCSDG}$$

(17)

The temperature and CM in the CSDG MOSFET exhibit an inverse correlation. Therefore, an increase in mobility is seen as temperature decreases. However, when temperature rises, increased mobility leads to more frequent electron collisions, thus reducing mobility and affecting other device parameters. Although the CSDG MOSFET is temperature tolerant, temperature should not be higher than 100°C to ensure device reliability and avoid damage.

#### THERMAL STABILITY IN CSDG MOSFET

One of the most important problems in electronic devices, especially MOSFETs, is thermal instability. Such instabilities may lead to poor performance outside the SOA due to variability in thermal variables arising from internal and external sources. Internal heating occurs due to the strong adhesion of passive elements in a microchip. Simultaneously, the external heats are generated from variations in environmental temperature and physical contact between MOSFET and its surroundings [22] and [23].

Many innovative ideas have been formulated for handling such thermal complications in MOSFETs. Another solution is integrating a control element in the MOSFET to regulate and respond to temperature variations. On the other hand, this may lower the integrity of such a device. The architecture of the CSDG MOSFET handles unprecedented thermal problems. It contains an empty internal system, which increases the airflow and decreases heat accumulation in the interior part. This modification results in better thermal stability than the previous models.

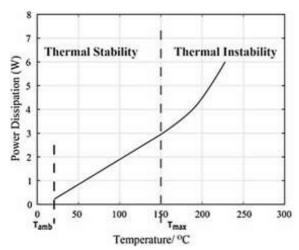

The CSDG MOSFET's round design also minimizes contact with the mounting board. The heat sink makes it possible to reduce the thermal transfer process of the board. The power dissipation and the circuit's performance in the absence of a heat sink:

$$M=R_{\ell}I^2 \tag{18}$$

M - Power dissipated

$$M_{max} = \frac{\Theta max - \Theta amb}{R \in}$$

(19)

$M_{\text{max}}$  -Maximum amount of power dissipated.

R€- TR of the CSDG MOSFET

$\Theta_{max}$  - the maximum operational temperature, and

$\Theta_{amb}$  - the ambient temperature.

Fig. 4: TR of CSDG MOSFET

In essence, this study offers a comprehensive analysis of the thermal effects on CSDG MOSFETs. It highlights the importance of thermal resistance modeling and its impact on device parameters under varying temperatures shown in figure 4. While the CSDG MOSFET exhibits improved thermal stability, accommodating both internal and external heat generation, challenges remain in analyzing the thermal noise and its impact on device performance. Future research will focus on enhancing the CSDG MOSFET's thermal stability and developing more robust models for thermal noise in the context of nanotechnology and VLSI applications.

#### Algorithm

## 1. Initialize Constants and Parameters

Set the Boltzmann constant **H**.

Set the charge of an electron  $\mathbf{q}$ .

Define the MOSFET parameters like carrier mobility CM, gate-source voltage  $V_{GS}$ , drain-source voltage  $V_{DS}$ , channel length  $W^2$ , channel width Z, oxide capacitance per unit area Cox, and threshold voltage Vth.

## 2. Define the Temperature Range

Create a range of temperatures (e.g., from 0K to 300K) over which the analysis will be conducted.

#### 3. Prepare for Data Collection

Initialize arrays or lists to store the calculated values of drain current ( $Id\_arr$ ) and transconductance ( $g_{m\_arr}$ ).

## 4. Temperature-Dependent Analysis

For each temperature **T** in the defined temperature range:

Calculate "Threshold Voltage ( $V_{th\_T}$ )" Shift: Adjust the  $V_{th\_T}$  based on the current temperature T.

Calculate Drain Current  $(I_D)$ : Use the MOSFET parameters and the temperature-adjusted threshold voltage to calculate the drain current at the current temperature.

Calculate Transconductance  $(g_m)$ : Compute the transconductance using the MOSFET parameters, temperature-adjusted threshold voltage, and current temperature.

Store Calculated Values: Append the calculated values of  $I_D$  and  $g_m$  to their respective arrays or lists.

#### 5. **Plotting the Results**

**Drain Current vs. Temperature Plot:** a. Plot the temperatures against the calculated drain current values. b. Label the axes (Temperature and Drain Current) and provide a title for the plot.

**Transconductance vs. Temperature Plot:** a. Plot the temperatures against the calculated transconductance values. b. Label the axes (Temperature and Transconductance) and provide a title for the plot.

Display the plots for analysis.

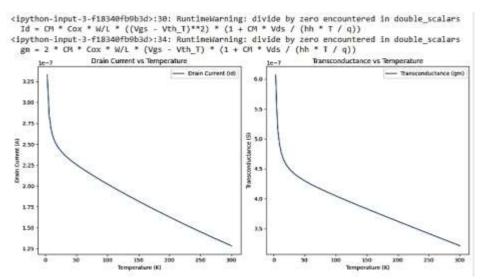

Fig. 5 (a) : Drain Current vs. Temperature Plot, Fig. 5 (b) : Transconductance vs. Temperature Plot

## **Drain Current vs. Temperature Plot**

Figure 5 (a) plot shows how the drain current ( $I_D$ ) varies as the temperature changes. A rise in temperature typically results in a simultaneous rise in the  $I_m$ . This is due to the enhanced CM at higher temperatures, which facilitates the movement of charge carriers (electrons or holes) across the MOSFET's channel. However, there's a limit to this behavior. Beyond a certain temperature, the performance might degrade due to increased carrier scattering and other thermal effects.

### Transconductance vs. Temperature Plot

Figure 5 (b) plot illustrates the change in transconductance  $(g_m)$  with temperature. Transconductance is a measure of the MOSFET's ability to control the input voltage, which is nothing but gate-source voltage and the output current. A higher transconductance indicates better control. The plot results reveal that transconductance could first increase due to increased carrier mobility with an increased temperature. However, as the temperature increases, transconductance declines, which may mean MOSFET's efficiency in controlling current flow decreases. This may be due to increased carrier scattering and thermal noise at higher temperatures.

# **Key Points**

**Thermal Sensitivity:** Both plots draw attention to the thermal characteristics of MOSFET. Identifying this sensitivity is essential for designing circuits that work effectively in different temperature ranges.

**Optimal Operating Temperature:** There is an optimal temperature range where the MOSFET operates most efficiently, managing both increased mobility (corresponding to increased current and transconductance) and too-high temperature, which increases scattering or noise.

**Design Considerations:** The unique design of such MOSFET should be considered for applications in very low or high temperatures to enable it to operate reliably. This may include the materials, device structure variants, and thermal management techniques.

#### Conclusion

The detailed analysis of CSDG MOSFET has led to exciting results related to the thermal aspects of technology dealing with MOSFET. The novel CSDG MOSFET architecture has been noted to overcome thermal instability issues, a common phenomenon in conventional designs. Thermal resistance, carrier mobility transconductance, and full-area total thermal stability of the CSDG MOSFET were investigated from different angles.

The analysis observed that CSDG MOSFET performs better in changing temperature conditions, especially where very low temperatures below the cryogenic level are required. A hollow structural core and cylindrical shape are some of the features that help reduce adverse heat effects inside and outside. The modifications enhance the keeping of a steady temperature and provide high reliability in operation for this device.

Additionally, the study gave information on mathematical modeling for specific critical parameters to CSDG MOSFET regarding their behavior under thermal stress. The device redesign alterations and modifications have successfully addressed challenges associated with the heat generated, inside or outside.

#### References

[1] M. Uchechukwu and V. Srivastava, "Channel length scaling pattern for cylindrical surrounding double gate MOSFET," IEEE Acc., 8 (2020) 1204-1210. https://doi.org/10.1109/ACCESS.2020.3006705

- [2] J. Verma, Y. Pratap, M. Gupta,S. Haldar and R. Gupta, "RF performance analysis and small signal parameter extraction of cylindrical surrounding double gate MOSFETs for submillimeter wave applications," 2<sup>nd</sup> Int. Con. on Dev. Cir. and Sys. (ICIMS), (2014) 1-5. https://doi.org/10.1109/ICIMSYST.2014.6926176

- [3] V. Srivastava, K. Yadav and G. Singh, "Design and performance analysis of cylindrical surrounding double-gate MOSFET for RF switch," Microelec. J., 42 (2011) 1124-1135. https://doi.org/10.1016/j.mejo.2011.07.003

- [4] A.Kranti and G.A. Armstrong, "Nonclassical channel design in MOSFETs for improving OTA gain-bandwidth trade-off,". IEEE Trans. Circuits Syst., 57 (2010) 3048–3054. https://doi.org/10.1109/INDICON.2015.7443481

- [5] S. Jaiswal and S. K. Gupta, "Digital Performance analysis of double gate MOSFET by incorporating core insulator architecture. Silicon Journal 32 (2022) 121-131. https://doi.org/10.1007/s12633-022-01811-7

- [6] V. Srivastava, K. Yadav and G. Singh, "Drain current and noise model of cylindrical surrounding double gate MOSFET for RF switch". Proc. Eng. 38 (20112) 517-521. https://doi.org/10.1016/J.PROENG.2012.06.064

- [7] O. Oyedeji and V. Srivastava, "Effect of radius on various parameters of cylindrical surrounding double-gate (CSDG) MOSFET". Int. jou. of eng. and tech. 7 (2018) 21-27. https://doi.org/10.14419/IJET.V7I4.10110

- [8] V. Srivastava, "Scaling effect on parameters of HfO<sub>2</sub> based CSDG MOSFET," Int. jou. of eng. and tech., 9 (2017) 420-426. https://doi.org/10.21817/IJET/2017/V9I1/170902322

- [9] N. Mittal, I. U. Khan, and N. K. Misra, "A low-power, wideband-tunable, nano dimension based CMOS LC ladder filter designed using G<sub>m</sub>C". Int. Jou. of Nano Dim., 14 (2023) 238-256. https://doi.org/10.22034/IJND.2023.1986547.2222

- [10] J. Verma, Y. Pratap, M. Gupta, S. Haldar and R. Gupta, "CSDG MOSFET: An advanced novel architecture for CMOS technology". Annual IEEE India Conference (INDICON), (2015) 1-5. https://doi.org/10.1109/INDICON.2015.7443481

- [11] https://doi.org/10.1109/ICEMELEC.2014.7151128

- [12] R. Kiran R., I. U. Khan and V. Purwar, "Temperature dependent performance analysis of high-K dielectric pocket-double cylindrical surrounding gate (HKG-DP-DCSG) & high K-dual material-double cylindrical surrounding gate (HKG-DM-DCSG) MOSFETs," Materials Today: Proc., (2023). https://doi.org/10.1016/j.matpr.2023.03.371

- [13] N. Gowthaman and V. Srivastava, "Parametric analysis of CSDG MOSFET with La<sub>2</sub>O<sub>3</sub> gate oxide: based on electrical field estimation," IEEE Acc., 9 (2021) 159421-159431. https://doi.org/10.1109/access.2021.3131980

- [14] Gowthaman N. and Srivastava V., "Mathematical modeling of drain current estimation in a CSDG MOSFET based on La<sub>2</sub>O<sub>3</sub> oxide layer with fabrication," A Nano. App. Nanom., vol. 12, pp. 1-13, 2022. https://doi.org/10.3390/nano12193374

- [15] A. Kumar A. and I. U. Khan, "Performance characterization of double material gate-all-around nanowire MOSFET," Proc. of Trends in Elec. and Hea. Info., (2022) 419-428. https://doi.org/10.2174/1876402913666210222141301

- [16] I.U. Khan, D. Balodi and N.K. Misra, "Low Power LC- quadrature VCO with superior phase noise performance in 0.13 μm RF-CMOS process for modern WLAN application," Circ. Sys. & Sig. Proc. (CSSP)-Springer Nat., 41 (2022) 2522–2540. https://doi.org/10.1007/s00034-021-01921-4

- [17] T. Cheung, M. Butson, and P. Yu, "Effects of temperature variation on MOSFET dosimetry". Phy. in med. and bio., 49 (2004) 191-204, 2004. https://doi.org/10.1088/0031-9155/49/13/N02

- [18] A. Gupta and S. Rai, "Reliability analysis of junction-less double gate (JLDG) MOSFET for analog/RF circuits for high linearity applications," Microelectron. Jou., 64 (2017) 60-68, 2017. https://doi.org/10.1016/j.mejo.2017.04.009

- [19] F. Nasri, M. Aissa, and H. Belmabrouk, "Microscale thermal conduction based on cattaneovernotte model in silicon on insulator and double gate MOSFETs," App. Th. Eng., 76 (2015) 206-211. https://doi.org/10.1016/J.APPLTHERMALENG.2014.11.038

- [20] Z. Ramezani, A. Orouji, S. Ghoreishi and I. Amiri, "A nano junctionless double-gate MOSFET by using the charge plasma concept to improve short-channel effects and frequency characteristics," Jou. of Elec. Mat., 48 (2019) 7487-7494. https://doi.org/10.1007/s11664-019-07559

- [21] A. Dargar and V. Srivastava, "Thickness modeling of short-channel cylindrical surrounding double- gate MOSFET at strong inversion using depletion depth analysis," Micro. and Nanos., 8 (2020) 124-136. https://doi.org/10.2174/1876402912666200831175936

- [22] W. Gan, R. Prentki, F. Liu, J. Bu, K. Luo, Q. Zhang, H. Zhu, W. Wang, T. Ye, H. Yin, Z. Wu and H. Guo, "Design and simulation of steep-slope silicon cold source FETs With effective carrier distribution model," IEEE Trans. on Elec. Dev., 67 (2020) 2243-2248. https://doi.org/10.1109/TED.2020.2988855

- [23] G. Qingguo, "Effect of back-gate voltage on the high-frequency performance of dual-gate MoS<sub>2</sub> transistors," Nanomaterials, 11 (2021) 1581-1594. https://doi.org/10.3390/nano11061594