# A STUDY ON LOW-POWER ALU DESIGN LEVERAGING VARIOUS ADVANCED OPTIMIZATION METHODS

## Nayakallu Vinod Kumar<sup>1</sup>, Dr.F.Vincy Lloyd<sup>2</sup>

<sup>1</sup>Research Scholar<sup>1</sup>, Bharath Institute of Higher Education and Research

D23EC501

vinod.nayakallu@gmail.com

<sup>2</sup>Professor<sup>2</sup>, Bharath Institute of Higher Education and Research

vincylloyd.ece@bharathuniv.ac

Abstract: VLSI technology has advanced significantly, and there are numerous effective methods for creating VLSI circuits. PTL, GDI (Gate Diffusion Input) methods, and CMOS are a few of the styles. The weaknesses of CMOS and PTL approaches can be eliminated by using the GDI technique to create low-power digital combinatorial circuits. This method maintains a low level of logic design complexity while lowering the amount of power consumed, propagation latency, and size of digital circuits. This paper discusses the benefits and limitations of GDI compared to CMOS design by comparing the various approaches with respect to layout area, transistor count, latency, and power dissipation.

**Keywords:** CMOS, Gate Diffusion Input (GDI), Pass Transistor Logic (PTL), Propagation delay,low-power.

#### 1. INTRODUCTION

The increased focus on high-speed, low-power embedded systems for smart phones, laptops, and other devices has caused VLSI technology to shrink to nanoscale levels, enabling the integration of more functionality onto a single chip. Over the past 20 years, a number of logic design methodologies have been developed in response to the desire to enhance the performance of logic circuits, which were previously based on conventional CMOS technology [6] [2, 3Pass-transistor logic (PTL) is a popular type of logic used in low-power digital circuitry. For nMOS, formal techniques for obtaining pass-transistor logic have been provided. They are based on the model in which the gates of nMOS transistors are subjected to a series of control signals. The sources of the n-transistors are subjected to an additional set of data signals. For low power digital circuits, the PTL (Pass Transistor Logic) is most commonly used.

PTL has several advantages over traditional CMOS design, including: 1) high speed because of small node capacitances; 2) low power dissipation since fewer transistors are used; and 3) less connectivity effects because of a compact area. But there are two main issues with PTL implementation: 1) Low drive current due to the single channel pass transistor's threshold voltage drop causes slow operation at lower power supplies; 2) significant direct path static power dissipation occurs because the regenerative inverter's high input voltage level is not  $V_{dd}$  and the PMOS device is not fully turned off. GDI is a technique that, in comparison to conventional CMOS design and current PTL techniques, is appropriate for designing quick, low power circuits with fewer transistors.

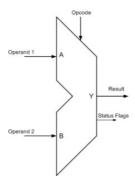

#### 1.1 ARITHMETIC LOGIC UNIT (ALU)

Inside the central processing unit (CPU) of every digital computer, the Arithmetic Logic Unit (ALU) functions as the heart. The ALU's job is to process data using logic and arithmetic

before sending it to the computer's memory. Power consumption will become a major issue as technology advances and design complexity rises since there are more transistors in use, which means that integrating them requires more energy and power [27]. Power dissipation is made up of two basic components, as demonstrated by equation 1 [28]. These are static and dynamic power dissipation. Furthermore, additional The use of transistors in Very Large-Scale Integration (VLSI) design will also result in an increase in area and a slight delay in the output execution [29].

## $P_{avg\ power} = P_{dynamic\ power} + P_{static\ power}$

The following operations are performed by an arithmetic unit: addition, addition with carry, subtraction, subtraction with borrow, and transfer functions. Initially, we create a single-bit Full Adder, followed by a 4-bit Ripple Carry Adder with four Full Adder numbers, and finally a 32-bit Ripple Carry Adder with eight 4-bit Ripple Carry Adder numbers. Next, we created a singlebit 4:1 multiplexer with 32 numbers. Fig. 6 displays the schematic of a 32-bit Arithmetic Unit. The circuit contains thirty-two multiplexers and a 32-bit parallel adder to create a 32-bit arithmetic unit[5].A and B are the two 32-bit inputs, while RESULT is the 33-bit output. Every multiplexer has a 4:1 size. S0 and S1 are the two common selection lines shared by all thirty-two multiplexers. The parallel adder's carry out is Cout, and its carry input is C\_in. Each multiplexer has thirty-two inputs: logic-0, logic-1, B-value, and Complemented B-value. The following arithmetic sum is used to calculate the circuit's output[26].

RESULT = A + Y + Cin

Figure 1. ALU Symbol

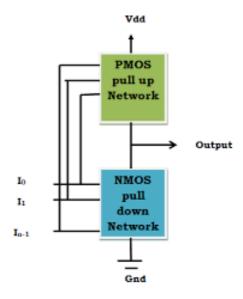

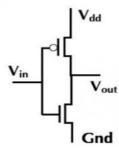

In this CMOS technology, both N-type and P-type transistors are used to realize logic functions. The N type and P type transistor are used for turns on and turn off a transistor. The design used simple switches. In this paper CMOS logic gates a collection of n-type MOSFETs is arranged in a pull down network (Vss or ground). In place of load resistor of NMOS logic gates, CMOS logic gates have a collection of p-type MOSFETs in a pull-up network, higher voltage rail (often named Vdd)[1]. Thus, if both a p-type and n-type transistor have their gates connected to the input, the p-type MOSFET will be on when the n-type MOSFET is off, and vice-versa as shown in the fig. 6 .In CMOS, when the input is high, NMOS gets ON and pulls down the output to ground(i.e., output becomes low). Whereas, when the input voltage is low, PMOS gets ON and pulls the output up from the ground (i.e., output becomes high). So we call PMOS as PULL UP transistor and NMOS as PULL DOWN transistor.

Figure 2.pullup and pull down

## 2. SOURCES OF POWER CONSUMPTION IN CMOS CIRCUITS

- 1. Short Circuit Power Consumption

- 2. Dynamic Power Consumption

- 3. Leakage(Static) Power Consumption

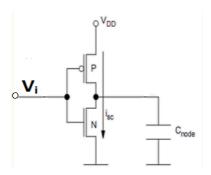

## **2.1 Short Circuit Power Consumption:**

This results due to direct path short circuit current which arises when both NMOS & MOS are simultaneously active and conduct current through resistive path between source and ground

Figure 3: Short circuit

Short Circuit Power Psc = Isc \* Vdd

Isc= short circuit current

Vdd=supply voltage

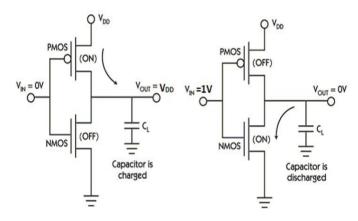

## 2.2Dynamic Power Consumption:

Dynamic power consumption in CMOS circuit is due to charging and dis-charging of load capacitance

Dynamic Power:

$P_{dyn} = 1/2 CLVdd2 \alpha f$

CL = load capacitance

$V_{dd} = Supply \ voltage$ f= frequency

Figure 4: Dynamic circuit

## 2.3:Leakage Power Consumption:

This power consumption takes place due to the flow of leakage currents through the device when it is in idle state.

Leakage Power Pleak =  $I_{leak}$ \*  $V_{dd}$

I<sub>leakage</sub>= Leakage current, V<sub>dd</sub>=Supply voltage

Total power consumption=  $P_{sc} + P_{dvn} + P_{leak}$

#### 3. DESIGN TECHNIQUES

#### 3.1 CMOS Technique:

The acronym for a complementary metal oxide semiconductor is CMOS. It uses transistors that are both PMOS and NMOS. PMOS transistors make up the pull-up network, and NMOS transistors make up the pull-down network. Electronic devices used PMOS and NMOS separately before CMOS. Among these, NMOS gained traction because of its quick functioning and cheaper price as compared to PMOS. One of NMOS's drawbacks is that it uses more static power. Circuit design is made more flexible when NMOS and PMOS are combined symmetrically in a single integrated circuit. Another benefit of CMOS is its low power consumption—it uses practically no power when it is in a static state. Transistor size, resilience, and dependable operation at low speeds are benefits of CMOS logic[4]

Figure 5. Basic CMOS cell

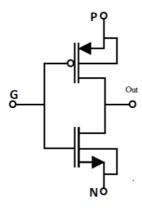

#### 3.2 GDI and m-GDI Technique:

GDI stands for Gate Diffusion Input. This design technique is used for reducing power in circuits. Along with power it also reduces the area of the circuit. The various logic functions such as AND, OR, etc. can be realized using only two transistors, one PMOS and one NMOS. The logic operations that can be implemented using a basic GDI cell are listed in the Table I.

Figure 6: Basic GDI cell

| Table 1 | Logic | functions | realized | using | basic | GDI | cell |  |

|---------|-------|-----------|----------|-------|-------|-----|------|--|

|         |       |           |          |       |       |     |      |  |

| N | P | G | OUT   | Function |

|---|---|---|-------|----------|

| 0 | В | A | AB    | F1       |

| В | 1 | A | A+B   | F2       |

| 1 | В | A | A+B   | OR       |

| В | 0 | A | AB    | AND      |

| С | В | A | AB+AC | MUX      |

| 0 | 1 | A | A     | NOT      |

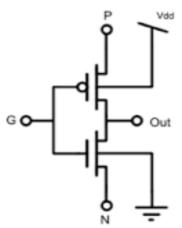

The GDI technology is modified and called m-GDI. This maintains the potential of all body terminals, meaning that the bodies of all PMOS and NMOS are connected to VDD and VSS in the proper manner.

Figure 7: Basic m-GDI cell

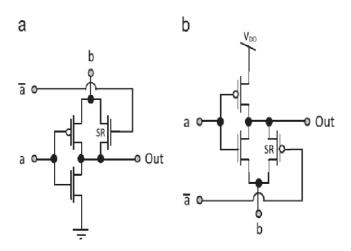

One limitation of the GDI and m-GDI techniques is that full swing output voltage cannot be achieved. The FS-GDI Method Full Swing Gate Diffusion Input is known as FS-GDI. It is a low power design strategy that minimises power usage and delays.

Compared to CMOS technology, full swing GDI technology operates more quickly [3]. This technology uses less transistors than the CMOS technique, even if it uses more than the m-GDI technique. It is a method for improving the output swing that is derived from the m-GDI method. It is used instead of swing restoration buffers to provide full swing output [4].

Figure 8: Basic FS-GDI cells

#### 4. PREVIOUS WORK

Some of the techniques to reduce power consumption in CMOS circuits are

- 1. Power gating

- 2. Clock gating

- 3. Transistor Sizing

- 4. Multi threshold technique

- 5. Variable threshold CMOS technique

It is possible to produce power decreasing at the circuit, module, or architectural levels [2]. Select information reason as the control rationale in a basic switch method, allowing additional information signal from the gate terminal [3]. An essential structure for ALU planning is the Full Adder. There are other types of FA planning that can be used in place of limiting forces, such as the 11 transistor FA (11T-FA), 10 transistor reduced power Full Adder (10T-FA), and Hybrid Full Adder (H-FA). FA operates in ultra-low mode with reduced power consumption by using subthreshold current [2], [3]. A 2:1 multiplexer and an XOR gate with close to ground power are used in the manufacturing of full adders. An ALU arrangement using the FinFET breakthrough features two electrically free gates. This reduces the circuit's complexity and, as a result of the leakage current decreasing, also lowers power consumption. The term "Fin" in Fin Field Effect Transistor (FinFET) invention refers to the thin silicon that forms the device's frame [4]. The Multiple Input Floating Gate - Metal Oxide Semiconductor (MIFG-MOS) re-configurable Arithmetic transistor's logic is used in the Logic Unit plan. This circuit's effectiveness is increased by a multitude of information. By monitoring the weighted sum of all factors taken into consideration, the MIFG-MOS transistor provides low and high situations. In addition to enhancing the circuit's display, MIFG-MOS transistors reduce the number of transistors and the circuit's unpredictable nature. They also restrict power distribution and delay [5]. When channel size scaling becomes unfavourable for circuit organisation, metal gates and dielectric K values greater than or equal to those should be promoted.

In [9] the authors have designed Power gated ALU. In [10] the authors have developed Low power arithmetic logic unit based sliced processor using GDI and MGDI, In [11] the authors have implemented FS-GDI approach with 65 nm technology for low power ALU, In [12] the authors have performed 8-Bit ALU Design using m-GDI Technique, In [13] the authors have simulated 8-bit ALU design using GDI techniques with less power and delay, In [14] the authors have proposed implementation of ALU using grapheme nano ribbon field-effect transistor and fin field-effect transistor. In [15] the authors have done MWCNTB On-chip Interconnects for ALU designed, In [16] the authors have designed 16-bit ALU Using Full-Swing GDI, In [17] the authors have analysis of ALU using Full Swing GDI Technique, In [18] the authors have done Performance Efficiency Analysis of ALU, In [19] the authors have Simulated Optimized Low Power ALU of 4-Bit Processor using 32nm Technology, In [20] the authors have done ALU Implementation Using CMOS Technology, In [21] the authors have provided Analysis of 8-Bit Low Power ALU in 45 nm Using GDI Technique, In [22] the authors have developed High Speed ALU in 45nm Using GDI Technique, In [23] the authors have designed ALU using VHDL for low power, In [24] the authors have implemented low power Brisk architecture of ALU, In [25] the authors have focused on building a Low Powered ALU with the implementation of Built-In Self-Test(BIST) mechanism for efficient arithmetic. and logical operations.

| S.No | Title                                                      | Technique      | Power consumption | Delay        |  |

|------|------------------------------------------------------------|----------------|-------------------|--------------|--|

| 1    |                                                            | CMOS           | 67.62x10-6        | 0.0635x10- 6 |  |

|      | Power and Delay Optimization                               | TG LOGIC       | 34.86x10-6        | 0.0285x10- 6 |  |

|      | of 8-Bit ALU using Various                                 | GDI LOGIC      | 32.45x10-6        | 3.5695x10- 6 |  |

|      | Techniques                                                 | MGDI<br>LOGIC  | 16.51x10-6        | 0.0013x10- 6 |  |

|      |                                                            | FSGDI<br>LOGIC | 12.23x10-6        | 0.0066x10- 6 |  |

| 2    | Design of PTL based Area Efficient and Low Power 4-bit ALU | PTL            | 2.58E+02          | 4.60E-10     |  |

|      | ALC                                                        | CMOS           | 1.20E+01          | 8.63E-10     |  |

| 3    | Design and Analysis of 8-Bit<br>Low Power ALU in 45 nm     | CMOS           | 1139.84           | 3.9399       |  |

|      | Using GDI Technique                                        | GDI            | 510.08            | 2.2229       |  |

| 4    | Design of 4 Bit ALU Using<br>Modified GDI Technology for   | GDI            | 0.214             | 0.933(ns)    |  |

|      | Power Reduction                                            | m-GDI          | 0.091             | 1.486(ns)    |  |

| 5    | 8-Bit ALU Design using m-GDI Technique                     | m-GDI          | 31.57 (uW)        | 4.57 ns)     |  |

#### **CONCLUSION**

Static power dissipation and dynamic power dissipation are the two categories into which power consumption in CMOS circuits is divided. Static power dissipation is not taken into consideration in today's CMOS circuits since it is so small in comparison to dynamic power dissipation. Dynamic power is intimately correlated with the power supply. With GDI implementation, there are fewer power supply to ground connections, which lowers dynamic power usage. This study examines and contrasts several methods for lowering the power consumption of ALU circuits. Of all the design strategies, the GDI technique turned out to have the best performance characteristics.

#### **References:**

- [1]. A. Morgenshtein, A. Fish, and I. Wagner, "Gate-diffusion input (GDI): a power-efficient method for digital combinatorial circuits," IEEE Trans. Very Large Scale Integr. Syst., vol. 10, no. 5, pp. 566–581, 2002, doi: 10.1109/TVLSI.2002.801578.

- [2]. M. A. Ahmed and M. A. Abdelghany, "Low power 4-Bit Arithmetic Logic Unit using Full-Swing GDI technique," in Proceedings of 2018 International Conference on Innovative Trends in Computer Engineering, ITCE 2018, 2018, vol. 2018– March, no. Itce, pp. 193–196. [3]. A. Morgenshtein, V. Yuzhaninov, A. Kovshilovsky, and A. Fish, "Fullswing gate diffusion input logic—Case-study of lowpower CLA adder design," Integration, the VLSI Journal, vol. 47, no. 1, pp. 62–70, Jan. 2014.

- [4]. A. Morgenshtein, I. Shwartz, and A. Fish, "Gate Diffusion Input logic in standard CMOS Nano scale process," 2010 IEEE 26th Convention of Electrical and Electronics Engineers in Israel, 2010.

- [5]. Y. Zhou and H. Guo, "Application specific low power ALU design," Proc. 5th Int. Conf. Embed. Ubiquitous Comput. EUC 2008, vol. 1, pp. 214–220, 2008, doi: 10.1109/EUC.2008.81

- [6] Shubham Sarkar, Hijal Chatterjee, PritamSaha, Manoj Biswas proposed "8- Bit ALU Designusing m-GDI Technique", Proceedings of the Fourth International Conference on Trends in Electronics and Informatics (ICOEI 2020) IEEE Xplore Part Number: CFP20J32-ART; ISBN: 978-1-7281-5518-0, 978-1-7281-5518-0/20 2020 IEEE

- [7]. K. Nehru, A. Shanmugam, G. Darmila thenmozhi, "Design of Low Power ALU Using 8T FA and PTL Based MUX Circuits", IEEE-International Conference On Advances In Engineering, Science And Management (ICAESM -2012) pp.978-981, March 30-31, 2012.

- [8]. G.Saranya, R.S.Kiruthika, "Optimized Design of an ALU Block using Architectural Level Power Optimization Techniques", IEEE-International Conference On Advances In Engineering, Science And Management (ICAESM -2011) pp.168-172.

- [9] K Prasad Babu, Dr. K.E. Sreenivasa Murthy, Dr. Dr. M.N. Giri Prasad, "Implementation of Power Gated Alu for Low Power Processor", https://www.biogecko.co.nz/admin/uploads/10904\_Biogeckoajournal for newzealandherpetology\_10-49-531.pdf

- [10] N. Subbulakshmi , R. Sravanthi , M. Subi Stalin , T. Swapna , T. Rajesh , Y. Greeshma ,"ALUSGDI: Low power arithmetic logic unit based sliced processor using GDI and MGDI", https://doi.org/10.1016/j.measen.2023.100842,www.sciencedirect.com/journal/measurement-sensors, Pg.no 1-9.

- [11]M.A. El-Bendary, F. Amer, Based on FS-GDI approach with 65 nm technology: low power ALU design, Int. J. Electron. (2022) 1–19, https://doi.org/10.1080/00207217.2022.2068195.

- [12] S. Sarkar, H. Chatterjee, P. Saha, M. Biswas, 8-Bit ALU Design using m-GDI Technique, in: 2020 4th International Conference on Trends in Electronics and Informatics (ICOEI) (48184, Tirunelveli, India, 2020, pp. 17–22, https://doi.org/10.1109/ICOEI48184.2020.9142881.

- [13] Harshmaniyadav Uday Panwar, Design of 8-bit ALU design using GDI techniques with less power and delay, Int. J. Recent Technol. Eng. 8 (4) (2019) 2277–3878, https://doi.org/10.35940/ijrte.D9544.118419.

- [14]D. Rebecca Florance, B. Prabhakar, Mishra Manoj Kumar, Design and implementation of ALU using graphene nanoribbon field-effect transistor and fin field-effect transistor, J. Nanomater. (2022) 17, https://doi.org/10.1155/2022/3487853, 2022, 3487853.

- [15] Takshashila Pathade, Yash Agrawal "Effective Low Power ALU Design with Incorporation of MWCNTB On-chip Interconnects", 2022 IEEE 24th Electronics Packaging Technology Conference (EPTC), 10.1109/EPTC56328.2022.10013187, 07-09 December 2022.

- [16] Poorvaja Harish,Dr. Kiran V, "Design of 16-bit ALU Using Full-Swing GDI",2022 IJRTI | Volume 7, Issue 10 | ISSN: 2456-3315, Pg.No 705-713.

- [17] Anand Krishnan S, K. B. Ramesh, "4-BIT Arithmetic Logic Unit (ALU) using Full Swing GDI Technique", Journal of Advancement in Electronics Design, Vol4, Issue 3, Pg. No 1-8.

- [18] Shylaja V., Shylaja V., Dr. K. Ezhilarasan, "Design and Performance Efficiency Analysis of a Low Power 4-bit Arithmetic Logic Unit", J. Electrical Systems 20-10s (2024):3712-3719, Pg. No 3712-3719.

- [19] K Prasad Babu, Dr. K.E. Sreenivasa Murthy, Dr. Dr. M.N. Giri Prasad, "Simulation of Optimized Low Power 4-Bit Processor using 32nm Technology", International Journal of Applied Engineering & Technology, Page No. 1345 1370.

- [20]Sharana Basavaraj B, Renuka S, Kavitha K, Krishna P,"ALU Implementation Using CMOS Technology",International Journal of Latest Technology in Engineering, Management & Applied Science (IJLTEMAS) Volume VII, Issue V, May 2018 | ISSN 2278-2540.

- [21] Wong Siong Hui, Siti Hawa Ruslan, "Design and Analysis of 8-Bit Low Power ALU in 45 nm Using GDI Technique", Evolution in Electrical and Electronic Engineering Vol. 2 No. 2 (2021) 110-119, DOI: https://doi.org/10.30880/eeee.2021.02.02.014.

- [22] Manish Kumar, Md. Anwar Hussain & L. L. K. Singh, "Design of a Low Power High Speed ALU in 45nm Using GDI Technique and Its Performance Comparison", Computer Networks and Information Technologies, pp. 458–463, 2011

- [23] Giridhari Muduli, Bibhudatt Pradhan, Manas Ranjan Jena, Snigdharani Nath, "Design of an Efficient Low Power 4-bit Arithmatic Logic Unit (ALU) Using VHDL", International Transaction of Electrical and Computer Engineers System, 2014, Vol. 2, No. 5, 144-148, DOI:10.12691/iteces-2-5-3

- [24] O. Vivedhini, C. Senthilkumar, "Design And Implementation Of Low-Poweralu For Brisk Architecture", International Journal of Creative Research Thoughts (IJCRT) 2023 IJCRT | Volume 11, Issue 9 September 2023 | ISSN: 2320-2882, Pg.No: c634-c645

- [25] M. Nagharjun and V. Ravi, "Low Powered Self-Testable ALU", IOP Conference Series: Materials Science and Engineering, Volume 1012, International Conference on Robotics, Intelligent Automation and Control Technologies (RIACT 2020) 2-3 October 2020, Chennai, India, DOI 10.1088/1757-899X/1012/1/012048, Pg.No: 1-13.

**N. Vinod Kumar** working as Assistant Professor in Ashoka Womens Engineering College. Currently he is doing his Ph.D in Bharat Institute of Higher Education and Research, Chennai, Tamilnadu. His-area of interest is VLSI & Embedded Systems.

Dr. Dr. F. VINCY LLOYD working as Professor in Bharat Institute of Higher Education and Research, Chennai, Tamilnadu. Her-area of interest is VLSI, Image Processing, IoT, Wireless Communications. She has published many papers in reputed journals