# A Novel Survey And RTL Design Of Formal Verification Of Mixed Signal Using Differential Fed Network

Dr. Vidhya D S.1, Dr. G. Raghavendra2

<sup>1</sup>Associate Professor Don Bosco College of Engineering Goa. University, Goa. ds.vidhya@dbcegoa.ac.in

<sup>2</sup>Associate Professor Sapthagiri College of Engineering, Bangalore. Visvesvaraya Technological University, Belagavi. meetraga81@gmail.com

The prime aim of the paper is to propose novel Formal Verification Framework (FVF) for mixed signal and thereby provide a cost effective solution for performing verification and validation of mixed signal circuits. To perform an in-depth investigation of the various standards formal verification models frequently adopted and introduced in prior studies and explore the research gap. To apply Artificial Neural Network (ANN) that will use differential feedback mechanism on analysis of mixed signal. To perform formal verification and validation of the proposed system and benchmark the outcome.

Keywords—Formal Verification, differential feedback.

### I. INTRODUCTION

In recent advancement in semiconductor has able to get small size integrated circuits, lesser weighted chips, which contains sea of transistors. SSI (Small scale integration), MSI (Medium scale integration and LSI (Large scale integration) are broadly classified under integrated technology [1]. Design, verification and testing are major requirement process to manufacture IC. Due to large number of transistors are stuffed in IC, the testing can be done by giving different input patterns to test the defects and analyze the response at the logic analyzer. Advancement in complex and problem in design emphasis for challenge in VLSI ICs. [1][2]. The verification issues exist in all the stages of the Analog mixed signal design. The implementation of analog circuits leads to verification challenges in terms of continuous electrical quantities which are sensitive towards signal noise, temperature and current leakage. The design process initialized with the design of every block and is verified separately to build a system which is expensive as the system is idealized at transistor level. The verification is performed by considering the transient or steady state response features of the system design in time or frequency domain. This process of exhaustive testing leads to difficulty in designing the large circuit.

The proposed study is based on the prime concept of formal verification, which is basically an act of evaluating the preciseness of the technique to be designed with consideration of the underlying formal specification both in the context of software and hardware. The usage of

format verification can be seen in various fields of studies e.g. digital circuits, cryptographic protocols, combinational circuits etc. The validation of such system is usually undertaken by furnishing the formal evidence on an abstract of mathematical model or an empirical model of the targeted system. One of the frequently adopted approaches of formal verification is model.

Checking that consists of a systematically exhaustive exploration of mathematical model. Although formal verification is studied with respect to software and hardware, but it possess various challenges in the industry specifically in hardware categories. At present, the adoption of formal verification is more on hardware industry and quite less on software industry. Hence, when it comes to design of mixed signal, formal verification possess a greater deal of challenges. Hence, this research proposal will discuss about prior works being done in this field followed by problems being identified and proposed solutions.

## II. BACKGROUND

In order to tackle the disadvantages of conventional simulation techniques, the formal verification technique is applied to verify analog mixed signal system. From previous twenty years, formal verification mechanism is very common approach to apply for digital hardware and software systems [3]. Last ten years, the research group have worked on different formal verification approaches. In 2004, Dang et al. [4] have worked on formal verification for time domain properties of mixed and analog circuits. The dynamic behavior is represented using differential algebraic approach. The research is limited to meet verification for larger systems. In 2006, Sofiene Tahar research work was significant towards verification method. In 2006 year, Tahar et al. [5] have discussed formal verification based on model checking methods for mixed signal and analog design. A symbolic verification algorithm for proving the properties of analog and mixed signal design has been worked in the year 2007 by Tahar et al. [6]. After gap of three years 2010, Tahar et al. [7] have proposed a a verification process for analog circuits considering noise and process variation. The mainly worked on a stochastic differential equation using MetiTarski tool automatic theorem. The theorem is based on a combination of resolution and a decision procedure for the theory of real closed fields.

After surveying many literatures, found some unique methods were adopted for verifying mixed signals. In 2012, Ulus and Sen [8] researched on analog mixed-signal design based on assertion-based verification process. When applying analog mixed signal to real world, the precision and tolerance are the main parameters to be consider for the facts. The boundary signal mechanism is to apply for tolerance and variation values of analog signals in assertions work was carried out by Ulus and Sen [8]. Formal verification for networked control system research work was done by Goswami et al. [9] in 2013. Discretized feedback control system, feedback delay and signal drop, and control requirements were discussed in that paper. Behavior modeling for mixed signal verification, mixed signal intellectual property (IP), validation for analog mixed signal and connectivity verification various methods were discussed in the same year by Liang [10]. Most recently (in 2014), Balasubramanian et al. [11] discussed on relative strengths, gaps and authors have presented the connect modules for analog mixed signal simulation.

After going through several methods for formal verification, it was observed that Artificial neural network (ANN) was one of the method for formal verification and its significance was

seen by Materka [12]. To analyze circuit parameters, feed forward neural network method was applied. The method gave high accuracy for verification and identification parameters. Hartel [13] from reputed University of Heidelberg, Germany applied artificial neural network method for formal verification method and it aims for performance .In same year , the author Manjunath et al. [14] have used differential neural network method for verification .The author adopted method for Ex-or function.

After reviewing all the papers, the majority of existing formal verification techniques is not computational cost effective. Adoption of neural network approach for verification was limited, so scalability of the formal verification process can be enhanced by adopting neural network approach. Neural network can perform parallel processing of multiple real valued signal inputs.

#### III. METHODOLOGYY

The proposed study will adopt mathematical modeling approach as a part of the research methodology. It has been closely observed that both validation as well as verification is slowly being emphasized by the research community with respect to contemporary integrated circuits. One of the challenging design issues in this respect will be to attain the time and area complexity in the test responses. While performing formal verification process of the mixed signal circuits. Therefore, the methodology is more inclined to achieving best reliability factor of the integrated circuits in the shortest range of time for enhancing the production and dispatching of the finally verified products in the markets.

In recent advance technologies, embedded IP cores are given importance with mixed signal. Formal verification methods are becoming more complex with the complex design. The detail formal verification is required for deep sub-micron technologies, otherwise specific error resulting in new Physical error in the design. A standalone verification method is required to increase the performance of complex design A several verification strategies have to be combined together to achieve a goal.

Thus, complementary error-oriented verification strategies will be developed and used, including the power supply current monitoring originally introduced for testing digital mixed-signal circuits as a method that requires dedicated verification pattern generation.

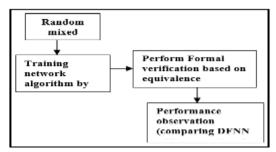

The new approach of artificial neural network introduction in verification of mixed signal is more appealing. By introduction of neural network offers good analysis of selected parameters of the circuit in the simple threshold decision method. Figure 1 shows the proposed schema of formal verification.

Figure 1: Proposed Formal Verification Schema

Random of mixed signal is generated by using MATLAB tool .Before applying to neural network design, data samples are to be normalized in preliminary investigation stage. The large changes in magnitude of input sample that differ by several orders can be avoided by using data normalization. In proposed research work, efficiency of the proposed test approach in detection of two major categories of error has been investigated. It can be intolerable error or parametric faults. The intolerable errors causes due to physical error in system design. Due to circuit parameters .Thus a proper design has to be analyze for the respective circuit. Due to undesired deviation in a circuit parameters leads to parametric faults.

In order to avoid error at the output, a proper design is required so that intolerable or parametric error can analyzed efficiently to increase the performance of the design .After training the data in a neural network design, a selected parameters can be taken for Analyzation. To evaluate the efficiency and performance of the proposed approach by detecting the errors in network design by comparing with reference design data with implemented design from network mixed signal ,a design will be considered for certain system.

An efficient neural network-based test approach to detection both intolerable physical errors as well as parametric error in analog and mixed-signal circuits using different methods of digital signal processing will be proposed. The board design contains neural network as its building block. Artificial neural networks can be made to learn different function after some training. The training period can be asymptotically reduced with a differential feedback. The differential feedback mechanism makes the overall training period lesser compared to the conventional networks at the same time maintaining the output quality in terms of square error. The differential feedback [16] is expected to make the runtime error arbitrarily small. In a differentially fed artificial neural networks, Reduction in the training period and smaller Square error, making them attractive for online usage. The function could be analog or digital; in any case, a single neuron can realize the function. The massive parallelism of neurons can give the output in one shot can be used in high-speed designs.

## IV. ALGORITHM DESCRIPTION

The algorithm will be tested with respect to time and space complexity to anticipate optimal algorithm efficiency. The proposed study is expected to exhibit lesser training period and optimal error reduction in formal verification process. Study is expected to mitigate the issues of formal verification and provide a fixed test-bed to verify analog, mixed, and digital signals.

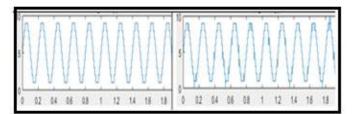

#### A .Generation of Mixed Signal

The mixed signal is generated based on mathematical equation and depends on sample number, network type and neuron number as shown in figure 2. Multiple type of mixed signal generated based on stabilized and un-stabilized state and it is grouped in to higher and lower electrical factors [15]. The time 't' and step functions ' $\tau$ ' are considered for input and four different mixed signals are generated at the output signal. Four different signals f1, f2, f3, and f4 are generated by considering a pseudorandom vector  $\alpha$ =0.3+0.6\*arb[1,1]. The f1 is stabilized with higher current and voltage factor and f2 is lower voltage and current factor with stabilized state.f3 and f4 are similar to f1 and f2 but un-stabilized higher and lower voltage and current factor [16].

Figure 2: Mixed signals

## **B.** Training network

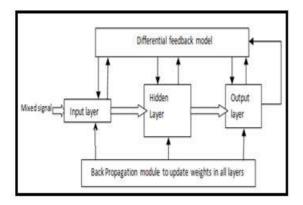

Figure 3: Differential feedback mechanism

The generated mixed signal from MATLAB tool is saved as text file. The text is stored as reference design using memory IP core.

The implemented design architecture view is shown in figure 3. The differential feedback mechanism is carried out using RTL code using back propagation to update the weights of input, hidden and output layer. The difference output from output layer is feedback to differential feedback model to adjust weights to reduce error so that improve accuracy of the mechanism.

## C. Formal Verification

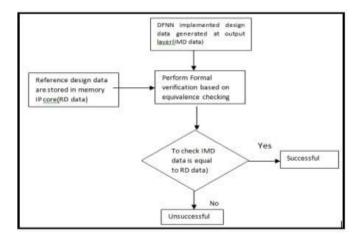

Figure 4: Performance of Formal verification

To check formal verification, the reference design and implemented design data's are compared using equivalence checking method. If the data are matched then verification is successful otherwise unsuccessful. The counter method is used to count the number of errors. Lesser the error then more accuracy. The flowchart for performance of formal verification is shown in figure 4.

To perform formal verification, the reference design data are saved in memory coefficient IP core are compared with implemented design data based on equivalence checking method. The introduction of counter check for successful or unsuccessful.

The differential output of neural network were fed to the differential fed back to remove the error, so differential fed mechanism has more accuracy when compared to conventional neural network. The performance can be improved by considering more number of sample data for training the network.

## V. CONCLUSION

This paper presented a novel Formal Verification Framework (FVF) tailored for mixed-signal circuits, aiming to deliver a cost-effective and efficient approach to verification and validation. Through a comprehensive analysis of existing formal verification models and standards, the study identified critical research gaps that were addressed by integrating an Artificial Neural Network (ANN) with a differential feedback mechanism. The proposed ANN-based approach enhances the analysis accuracy of mixed-signal behavior, enabling intelligent decision-making during the verification process. Formal validation and benchmarking of the framework demonstrated its effectiveness and reliability in improving verification coverage, reducing complexity, and minimizing development costs. Overall, the proposed FVF offers a scalable and robust solution for the formal verification of mixed-signal designs, paving the way for future research and industrial adoption.

#### VI. REFERENCES

[1] A.P.Godse, U.A.Bakshi, "Electronic circuits", Technical Publications, 744 pages, 2009

- [2] H. J. M. Veendrick, "Nanometer CMOS ICs: From basics to ASICs", Springer Science & Business Media, Application-specific integrated circuits, 762 pages, 2010

- [3] L. Yin, "Formal Verification and in-Situ Test of Analog and Mixed-Signal Circuits", doctoral thesis of Texas A&M University, 2012

- [4] T. Dang, A. Donze, O. Maler, "Verification of Analog and Mixed-Signal Circuits using Hybrid System Techniques", Springer, 2004

- [5] S. Tahar, M. H. Zaki, and G. Bois, "Formal Verification of Analog and Mixed Signal Designs: Survey and Comparison", IEEE North-east Workshop on Circuits and Systems, pp.281-284, 2006

- [6] S. Tahar, G. A. Sammane, M.H. Zaki, "A Symbolic Methodology for the Verification of Analog and Mixed Signal Designs", IEEE-Design, Automation & Test in Europe Conference, pp.1-6, 2007

- [7] S. Tahar, R. Narayanan, B. Akbarpour, "Formal Verification of Analog Circuits in the Presence of Noise and Process Variation", IEEE-Design, Automation & Test in Europe Conference, pp.1309-1312, 2010

- [8] D. Ulus, A. Sen, "Using Haloes in Mixed-Signal Assertion Based Verification", IEEE-High Level Design validation and Test Workshop, pp. 49-55, 2012

- [9] D. Goswami, S. Chakraborty, P. Bhaduri and S.K. Mitter, "Characterizing Feedback Signal Drop Patterns in Formal Verification of Networked Control Systems", IEEE Conference on Computer Aided Control System Design, pp.13-18, 2013

- [10] C. Liang, "Mixed-Signal Verification Methods for Multi-Power Mixed-Signal System-on-Chip (SoC) Design", IEEE10<sup>th</sup> International Conference on ASIC, pp.1-4, 2013

- [11] L. Balasubramanian, B. K. Poluri, "Efficient methods for analog mixed signal Verification", DVCON-Conference and Exhibition on Design and verification, 2014

- [12] A. Materka and M. Strzelecki, "Parametric Testing of Mixed-Signal Circuits by ANN processing of transient responses", Journal of Electronic Testing, Vol.9, Iss.1-2, pp.187-202, 1996

- [13] A. Hartel, "Improving and Testing a Mixed-Signal VLSI Neural Network Chip", Thesis of University of Heidelberg, Germany, 2010

- [14] R. Manjunath, S. Vasudev, N. Udupa, "Differential learning algorithm for Artificial Neural Networks", International Journal of Computer Applications, Vol.1, No. 18, 2010

- [15] Vidhya D.S and R. Manjunath, "Research Trends in Formal Verification Process for Analog and Mixed Signal Design", International Journal of Computer Applications (0975 8887) Volume 109 No. 11, January 2015.

- [16] Vidhya, D. S., and Manjunath Ramachandra. "A Novel Design in Formal Verification Corresponding to Mixed Signals by Differential Learning." Computer Science On-line Conference. Springer, Cham, 2017.