# Design of an Active Inductor Based Enhanced CMOS LNA Circuit

# Shinjini Yadav, Saima Beg

Department of Electronics and Communication Engineering, Integral University, Lucknow, UP, India

Email: yadavshinjini@gmail.com

The current state of radio frequency identification (RFID) technology is protocol specific to modern applications. In order to enable tag communication using a single protocol, the reader must either be universal or avoided when using a common RFID standard in Internet of Things (IoT) devices. For 2.4 GHz IoT RFID applications, it is recommended to use a complementary metal oxide semiconductor (CMOS) low noise amplifier (LNA). The limitations associated with spiral inductor-based LNAs, such as their large die area, low Q factor, and limited tuning flexibility, remain unresolved. Consequently, an LNA is developed using an inductor-free approach on a 90nm CMOS process. The post-layout simulation shows a 2.4 GHz bandwidth, 19 dB gain, and 1.55 dB noise figure. The LNA uses a relatively little amount of power from a 1.5 V source is just 1.08 mW. The inductor-less method has allowed for the achievement of an extremely tiny layout measuring 127.7  $\mu m2$ .

Keywords: Low energy technology, stabilization, LNA, I/O matching

#### 1. Introduction

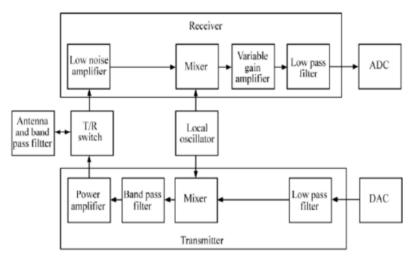

Currently, the most dependable wireless communication standard for exchanging and storing information is radio frequency identification. RFID communication uses HF to microwave frequencies to exchange information between tags, readers, and information processing units [1]. All things considered, the cost of the reader is nearly equal to the whole cost of the system, which is a barrier to RFID use in internet of things (IoT) devices. Proposing a resolution to this concern, modern IEEE 802.11b protocol-based RFID recommends replacing the RFID reader with wireless network interface cards employing the IPV6 concept [2]. The components of an IoT RFID front-end are illustrated in Figure 1. An LNA, which manages the raw signal that the antenna has intercepted, is regarded as a highly important block. A tank circuit is necessary for an LNA design; however, onchip inductors are not recommended for usage in microwave circuits due to high loss and larger die size. For many fascinating applications, inductors are thought to be essential for the analogue front-end of all radio frequency systems [3–12]. On-chip inductors are typically used in RF regime amplifiers and

filters. However, parasitic losses affect inductors on silicon substrates, which lowers the performance of RF devices. Furthermore, issues such as die size, reduced quality (Q) factor, restricted tuning flexibility, and so forth force designers of radio frequency integrated circuits (RFICs) to consider alternate [6].

Figure 1 The front-end of IoT RFID.

MOS based active inductors are offered as a solution to overcome the drawbacks. The advantage of correctly adjusting these active inducers is that it can offset the impacts of Process-Voltage-Temperature (PVT) change. Furthermore, in comparison to its on-chip equivalent, they may provide a better quality factor and greater inductance value at just 10% of the die [13]. As such, passive inductors are no longer the first choice of RFIC designers, despite the tremendous developments in integrated circuit technologies.

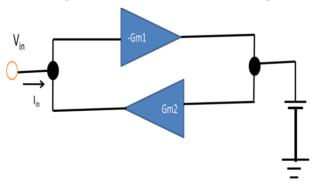

As seen in Fig. 2, the impression of active inductor which is a result of gyrator model [14, 15]. This circuit has two ports and is made up of two transconductors coupled in a negative feedback loop.

#### 2. Methodology, Result and Discussion:

1 Gbps of data is sent on the 3.1–10.6 GHz Ultra-Wideband (UWB) bandwidth. It uses less electricity because it is connected to a quiet environment. UWB technology is used in low-power, high-data-rate applications such as 5G networks, biomedical transceivers, and sensor nodes. The challenge of LNA design in the UWB range is to retain linear response, impedance matching, high gain, and low noise figure while adhering to stability restrictions.

It has been found that common source based biassing in CMOS-based circuits is capable of meeting the aforementioned conditions.

Device body potential's effect is defined as:

$$V_{TH} = V_{TH0} + \gamma \left( \sqrt{|2 \emptyset_f| + V_{SB}} - \sqrt{|2 \emptyset_f|} \right)$$

$V_{TH0}$ : is the threshold voltage at zero source-bulk potential, and  $\gamma$  is a body-effect parameter, which is a process factor. where  $\phi f$ : is the work function of a semiconductor. The CG-CS topologies configured as current reuse are used by the proposed UWBLNA.

The input CG stage aids in matching the input across a broad frequency range. To improve output impedance match and achieve a flat, high power gain, the output CS stage is employed.

A biassing technique is used to maximise the CG stage gain in order to get broader enhanced gain.

The series gate peaking approach is employed to improve the gain of the CG and CS stages, hence improving the LNA gain. The proposed LNA's gain was managed by the use of inductive resistive shunt peaking. The intended LNA gain formula, which takes total transconductance into account, is given by the following equation  $(g_{mT1})$ :

$$A = \frac{(1 + g_{mT1}r_{o1})g_{m2}((R_{d2} + j\omega L_{d2})//R_{out})}{(r_{o1} + j\omega L_{d1})j\omega C_{gs2}}$$

By employing this biasing technique, the input-referred components of gate thermal and flicker noise are minimized, while maximizing the device transconductance [1].

Furthermore, an inter-stage LC matching network is utilized to enhance noise immunity and improve performance [2].

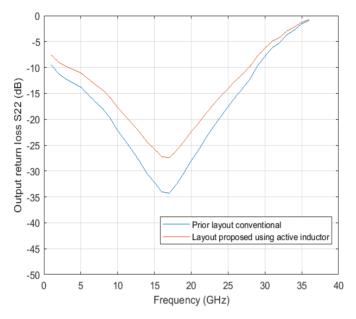

The parallel inductor peaking approach is used to adopt a good value of output corresponding for output return loss. The inductive resistive network's controlling quality factor determines the stages matching bandwidth. Furthermore, in order to increase the output impedance matching's bandwidth, a resistive termination with a parallel output resistance was included at the output in the suggested design.

### 3. Conventional LNA design:

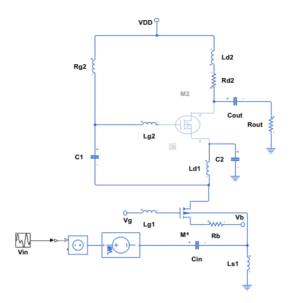

The LNA is modelled and designed using 130nm CMOS technology.

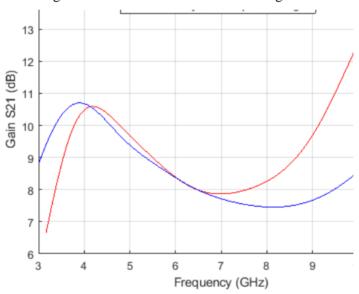

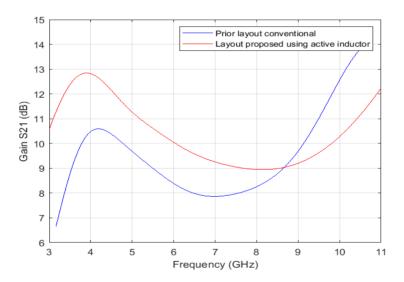

Gain in Power and Noise Level The intended range from 3.1 GHz to 10.6 GHz is covered by the 9.75±2.75 dB gain of the planned LNA. Techniques like FBB and inductive peaking are responsible for this increase in power gain.

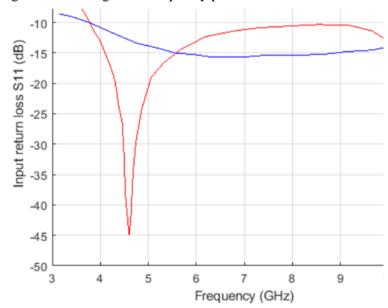

Figure 2 displays the results of the LNA achieved gain simulation. The outcomes of the preand post-layout simulations are compared. Fig. 3 displays the post-layout results compared to the prelayout results of NF. The minimal post-layout noise figure of this very low-power LNA is 3.9 dB. The bulk conductance's presence boosts this LNA increase without requiring excessive power usage. To achieve forward biassing, the bulk potential is adjusted to have zero passing current in the bulk. In order to properly utilise biassing, a series resistive (Rb) current blocking was included to assure lower scrounging losses and prevent power indulgence in bulk.

Figure 2 Conventional LNA circuit design

Figure 3 Gain vs frequency plot for Conventional LNA  $\,$

Figure 4 Noise Figure vs frequency plot for Conventional LNA

Figure 5 Input return loss vs frequency plot for Conventional LNA

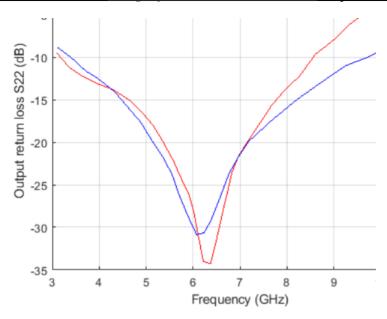

Figure 6 Output return loss vs frequency plot for Conventional LNA

## 4. LNA Design Proposed

In microwave circuits, on-chip inductors are not recommended due to increased loss and bigger die size; nonetheless, an LNA circuit requires a tank circuit.

The performance of RF devices is lowered by parasitic losses inductors in silicon substrates.

MOS based active inductors are offered as a solution to overcome the drawbacks.

The gyrator model has an impact on how the active inductor is perceived.

Figure 7 The perception of a gyrator.

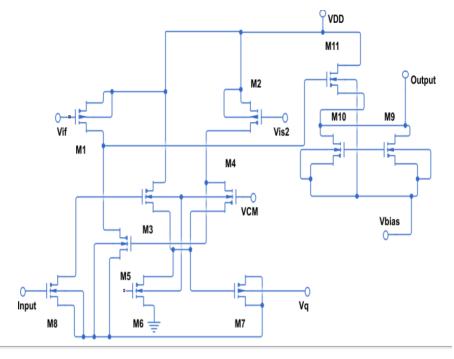

Figure 8 Proposed LNA circuit design

- LNA schematic:

- M1, M3, M4 (10/0.36),

- M2 (30/0.36),

- **M**5, M6 (3/0.36), M7, M8, M9 10 (0.12/0.36), M11 (1/0.36),

- VIF, Vis/2,

- Vis = 0.85V,

- Vq = 0.7V,

- Vcm = 0.7V,

- VDD = 1.5V.

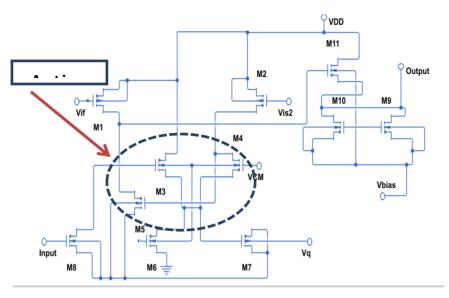

Figure 9 Location of active inductor in proposed LNA design.

The very low admittance at the resonance frequency of an active inductor makes it possible to use it as a tank circuit. The active inductor circuit schematic for the suggested LNA is shown in Fig. In this instance, the non-inverting transconductor (GM1) represented by M3 and M4 has an input voltage of V1 and an output current of V3. M5, an inverting transconductor (-GM2), has an output current of V1 and an input voltage of V3. The gyrator core is made up of these two transconductances. At node 3, the parasitic capacitor C1 and the gyrator combine to form an active inductor. Through analysis of the inductor equivalent depicted in the figure, the component values are determined:

$$\begin{split} L_{eq} &= \frac{GC_3}{g_{m1}g_{m2}g_{m3}} \approx \frac{C_3}{0.5g_{m1}g_{m3}} \\ &r_{loss} = \frac{g_3}{0.5g_{m1}g_{m3}} \\ &C_p = C_1 \\ &R_p = \frac{1}{g_1} \end{split}$$

Figure 10 Position of stages in proposed LNA circuit with input buffer active inductor and output buffer

Figure 11 Comparison of gain versus frequency plots for both Conventional and proposed Low-Noise Amplifiers (LNAs).

Figure 12 Noise figure vs frequency plot for Conventional and proposed LNA

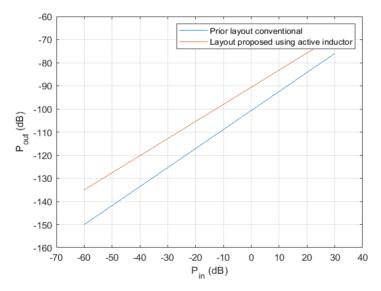

Figure 13 Pout vs Pin plot for Conventional and proposed LNA

Figure 14 Output return loss vs frequency plot for Conventional and proposed LNA

#### 5. Conclusion:

1 Gbps of data is sent on the 3.1–10.6 GHz Ultra-Wideband (UWB) bandwidth. It uses less electricity because it is connected to a quiet environment. UWB technology is used in low-power, high-data-rate applications such as 5G networks, biomedical transceivers, and sensor nodes. The challenge of LNA design in the UWB range is to retain linear response, impedance matching, high gain, and low noise figure while adhering to stability restrictions. It is found that CMOS-based circuits with active inductors can meet the aforementioned requirements.

### Acknowledgement:

The authors express their gratitude to Integral University, Lucknow, for assigning the manuscript number IU/R&D/2024-MCN0002510 to the current research endeavor.

#### References

- 1. Wei-Chang Li, Chao- Shiun Wang and Chorng-Kuang Wang "A 2.4-GHz/3.5-GHz/5-GHz Multi-Band LNA with Complementary" 1-4244-0180-1/06/\$20.00 ©2006 IEEE

- 2. Laichun Yang, Yuexing Yan, "A High Gain Fully Integrated CMOS LNA for WLAN and Bluetooth Application", IEEE conference on Electron Devices and Solid State. Jun.2013.

- 3. Thomas H. Lee, "The Design of CMOS Radio-Frequency Integrated Circuit," Cambridge University Press, 1998.

- Erick Emmanuel Djoumessi and Ke Wu, "Dual-Band Low-Noise Amplifier Using Step-Impedance Resonator (SIR) Technique for Wireless System Applications", Proceedings of the 39th European Microwave Conference; , Rome, Italy, 978-2-87487-011-8 EuMA 29

Nanotechnology Perceptions Vol. 20 No. S4 (2024)

- September, Page(s): 1307-1310 October 2009.

- 5. D. Shaeffer and T. Lee, "A 1.5V, 1.5 GHz CMOS low noise amplifier," IEEE J. Solid-State Circuits, vol. 32, May 1997.

- 6. Akhchaf, S. Khoulji, M. Essayed "A Novel And Single Chip Tri-Band Lownoise Amplifier For Wlan, Wifi And Wimax Receivers" International Journal of Computer Science & Information Technology (IJCSIT) Vol 4, No 6, December 2012.

- 7. Hyunki Jung et. al., "A 30–40 GHz CMOS Receiver Front-End with 5.9 dB NF and 16.5 dB Conversion Gain for Broadband Spectrum Sensing Applications", Electronics 2019, 8, 593.

- 8. K. Yamasaki, S. Yoshizawa, Y. Minami, T. Asai, Y. Nakano and M. Kuroda, "Compactsize numeric display pager with new receiving system," in NEC Rec. & Develop.,vol. 33, no. 1, pp. 73-81, January 1992.

- 9. A. Burt, "Direct conversion receivers come of age in the paging world," in GECRev., vol. 7, no. 3, pp. 156-160, 1992.

- 10. S. Tanaka, A. Nakajima, J. Nakagawa and A. Nakagoshi, "High-frequency, low-voltagecircuit technology for VHF paging receiver," IEICE Trans. Fundamentals of Electronics, Communication and Computer Science, vol. E76-A, no.2, pp. 156-163, 1993.

- 11. A. Mashhour, W. Domino and N. Beamish, "On the direct conversion receiver' atutorial," Microwave Journal, pp. 114-128, June 2001.

- 12. Jin-Fa Chang, et .al., "3-9 GHz CMOS LNA Using Body Floating and Self-Bias Technique for Sub-6 GHz 5G Communications". IEEE 2021.

- 13. Sakshi Singh Dangi et. al., "A Review on Lna Design For Wi -Max Applications", International Research Journal of Modernization in Engineering Technology and Science, Volume:03/Issue:09/September-2021.

- 14. Mahesh Mudavath et. al., "Design of Cryogenic CMOS LNAs for Space Communications", Journal of Physics, ICCIEA 2020.

- 15. Rajani Bisht and S. Qureshi, "Design of Low-Power Reconfigurable Low-Noise Amplifier with Enhanced Linearity", IEEE 2019.

- 16. Roman Yu. Musenov et. al., "The S- and C- band Low-power CMOS LNA Using the Current-reuse Technique", IEEE 2021.

- 17. L. Belostotski and J. W. Haslett, "Noise figure optimization of inductively degenerated CMOS LNAs with integrated gate inductors," IEEE Transactions on Circuits and Systems-I: Regular Paper, vol. 53, no. 7, 2006.

- 18. J. S. Goo, H. T. Ahn, D. J. Ladwig, Z. Yu, T. H. Lee and R. Dutton, "A noise optimization technique for integrated low-noise amplifiers," IEEE Journal of Solid-State Circuits, vol. 37, no. 8, pp. 994-1002, August 2002.

- 19. B. Razavi, "Architectures and circuits for RF CMOS receivers," IEEE Custom IntegratedCircuits Conference, pp. 393-400, May 1998.

- 20. Deepak Balodi, ArunimaVerma and PA Govidacharyulu, "A high gain low noise amplifier design & comparative analysis with other MOS-topologies for Bluetooth applications at 130nm CMOS," 2016 IEEE Industrial Electronics and Applications Conference (IEACon), IEEE Xplore, pp 378-383, 2016.

- 21. R. Salmeh, "A low voltage / low power 1.5 GHz low noise amplifier," IEEE SarnoffSymposium on Advances in Wired and Wireless Communications, pp. 81-84, April 2005.

- 22. AmgothuLaxmi Divya1, Mahesh Mudavath, Ch S Ranadheer, Mohamed Afzal andR.Venkateswarlu, "Low Noise Amplifier Design and Performance Analysis of RFFront-End for Narrow Band Receivers," Journal of Physics: Conference Series, IOP Publishing, ICCIEA 2020.

- 23. AayushAneja et. al., "Design and analysis of a 1.1 and 2.4 GHz concurrent dual-band low noise amplifier for multiband radios", AEU International Journal of Electronics and

- Communications, Volume 134, May 2021, 153654.

- 24. H. -H. Chen, W. -C. Cheng, C. -H. Hsieh and Z. -M. Tsai, "Design and Analysis of High-Gain and Compact Single-Input Differential-Output Low Noise Amplifier for 5G Applications," in IEEE Microwave and Wireless Components Letters, vol. 32, no. 6, pp. 535-538, June 2022, doi: 10.1109/LMWC.2022.3149033.

- 25. Roobert, A.A., Rani, D.G.N. Design and analysis of a sleep and wake-up CMOS low noise amplifier for 5G applications. Telecommun Syst 76, 461–470 (2021). https://doi.org/10.1007/s11235-020-00729-y

- 26. Amir Hossein Kazemi, Mohsen Hayati, "Design and analysis of a flat gain and linear low noise amplifier using modified current reused structure with feedforward structure", Integration, Volume 81, 2021, Pages 123-136, ISSN 0167-9260, https://doi.org/10.1016/j.vlsi.2021.05.013...